-

- 連絡先

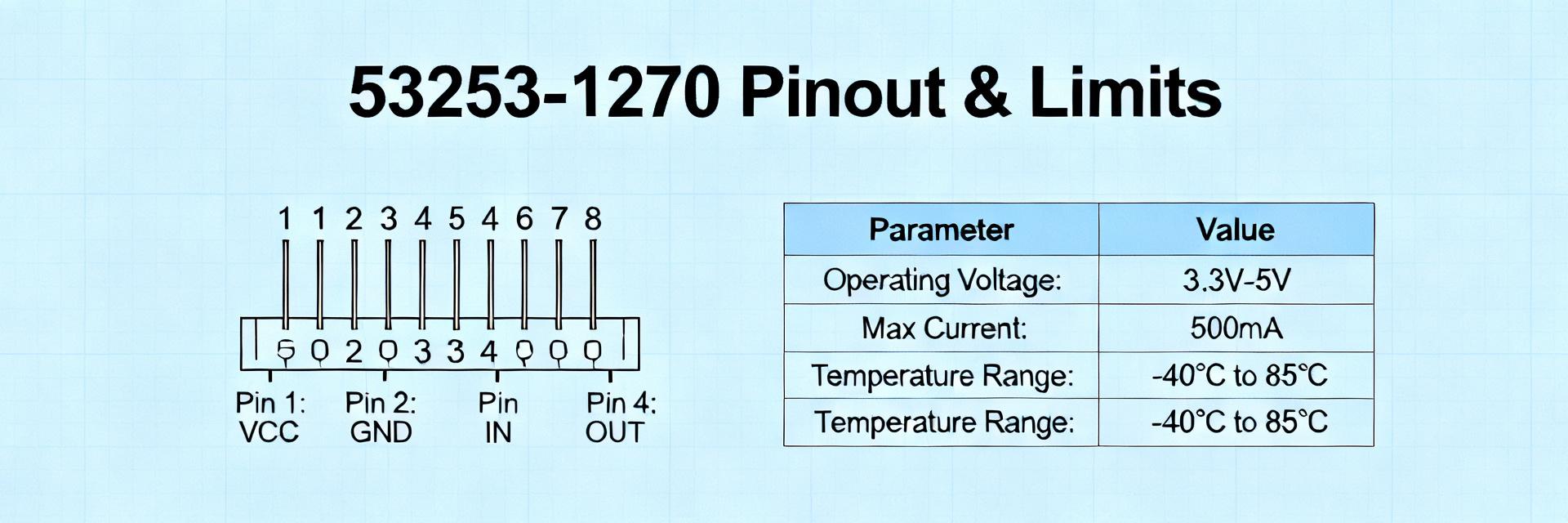

53253-1270 ピン配列及び電気的仕様 - クイックデータパック

要点: このクイックデータパックは、設計者がレイアウトと検証を迅速化できるよう、重要な 53253-1270 のピン配置と電気的制限を凝縮しています。

根拠: 凝縮されたリファレンスと一般的な検証手順により、コネクタ統合プロジェクトの平均反復時間が短縮されます。

説明: 回路図作成、フットプリント作成、および最初のボードの立ち上げ時に、以下の1ページマップを使用して、方向ミスや後工程での手直しを回避してください。

要点: このドキュメントは、完全な認証詳細ではなく、実用的でテスト可能な項目に焦点を当てています。 根拠: 最終的な調達と認定については、常に公式の 53253-1270 データシート と値を照合してください。 説明: このパックを設計決定の迅速なリファレンスとして扱い、承認やコンプライアンスチェックのためにデータシートを手元に置いておいてください。

部品の概要と典型的な用途(背景)

1.1 部品ID、共通バリアント、および典型的な用途

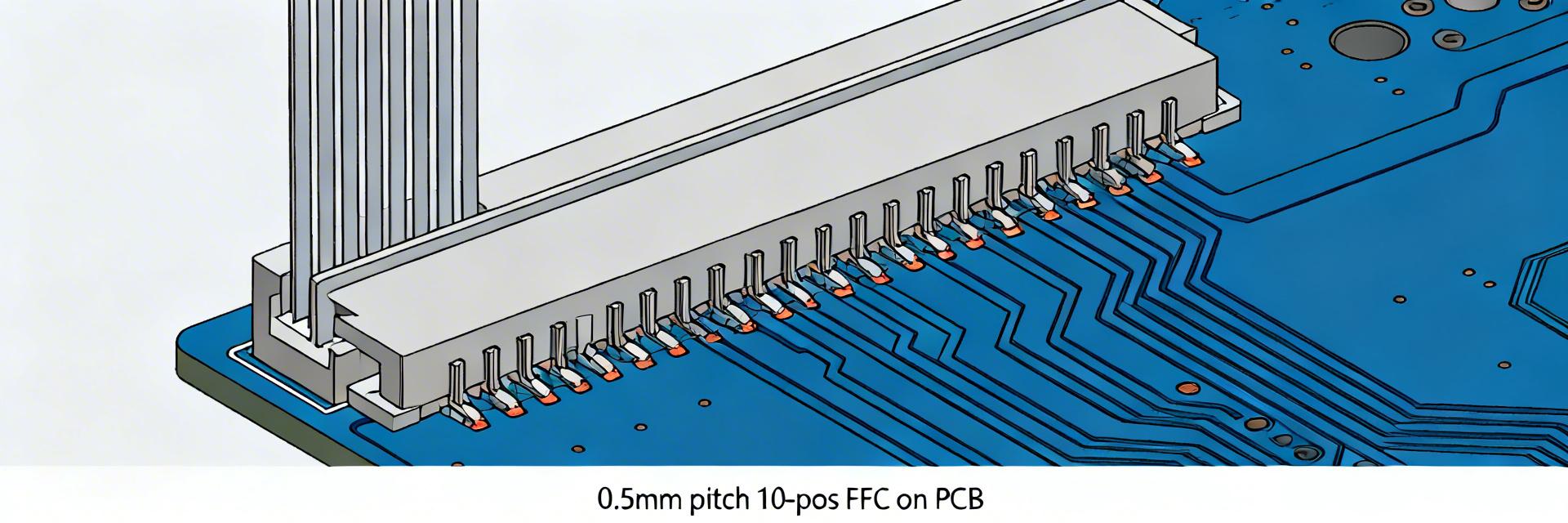

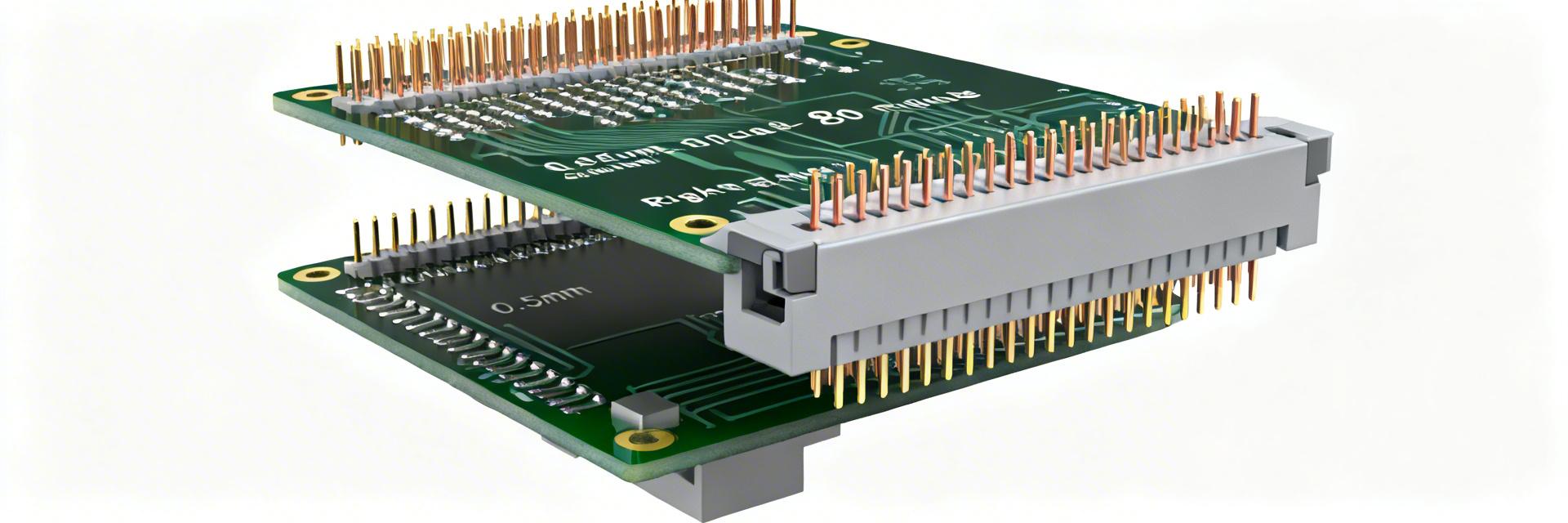

要点: 53253-1270 は、基板対基板および電線対基板の信号相互接続として一般的に使用される、2.00 mm ピッチの薄型長方形ヘッダーファミリーです。 根拠: バリアントには、ストレート対ライトアングル、シュラウド付き対オープンハウジングがあり、列数は嵌合構成によって異なります。 説明: 典型的な用途は、中密度のI/O、制御基板用信号ヘッダー、およびコンパクトなアセンブリにおける低電流の電力分配です。

- ユースケース: 基板対基板メザニン、ケーブルハーネスインターフェース、テスト治具、およびディスクリート信号ブレイクアウトヘッダー。

注:注文コードと機械図面については、公式の 53253-1270 データシート を参照してください。

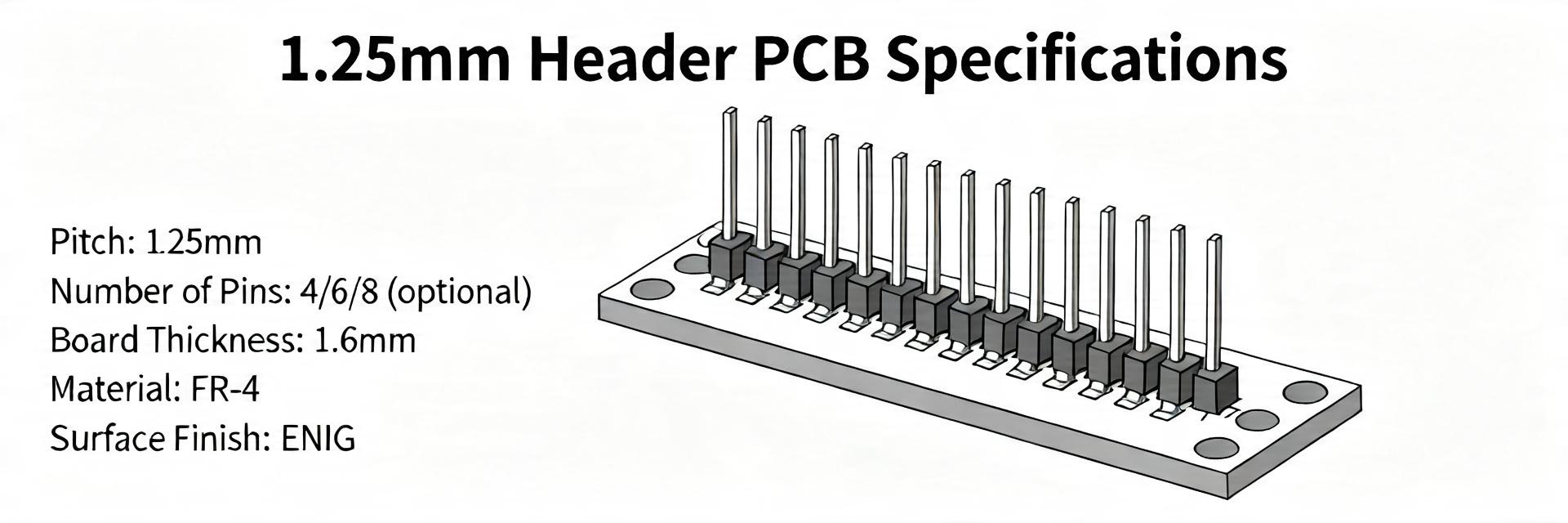

1.2 主要な機械的寸法とフットプリントの概要

要点: PCBレイアウトに影響を与える重要な寸法は、ピッチ、列間隔、ピンの突出、およびボディの高さです。 根拠: 設計者は、ピッチ(公称 2.00 mm)、PCBから嵌合面までの期待されるピンの長さ、および隣接するコンポーネントのキープアウト高さを抽出する必要があります。 説明: ルーティングの前に、迅速な配置と干渉チェックのために、寸法表と簡単な上面/側面スケッチを作成してください。

| 寸法 | 公称値 | 許容差 |

|---|---|---|

| ピッチ | 2.00 mm | ±0.10 mm |

| 列間隔 | — (バリアントにより異なる) | データシート参照 |

| ピンの長さ (PCBまで) | ~2.5–4.0 mm | ±0.2 mm |

ピン配置マッピングとナンバリングロジック(データ分析)

2.1 ピンナンバリング図と信号割り当て

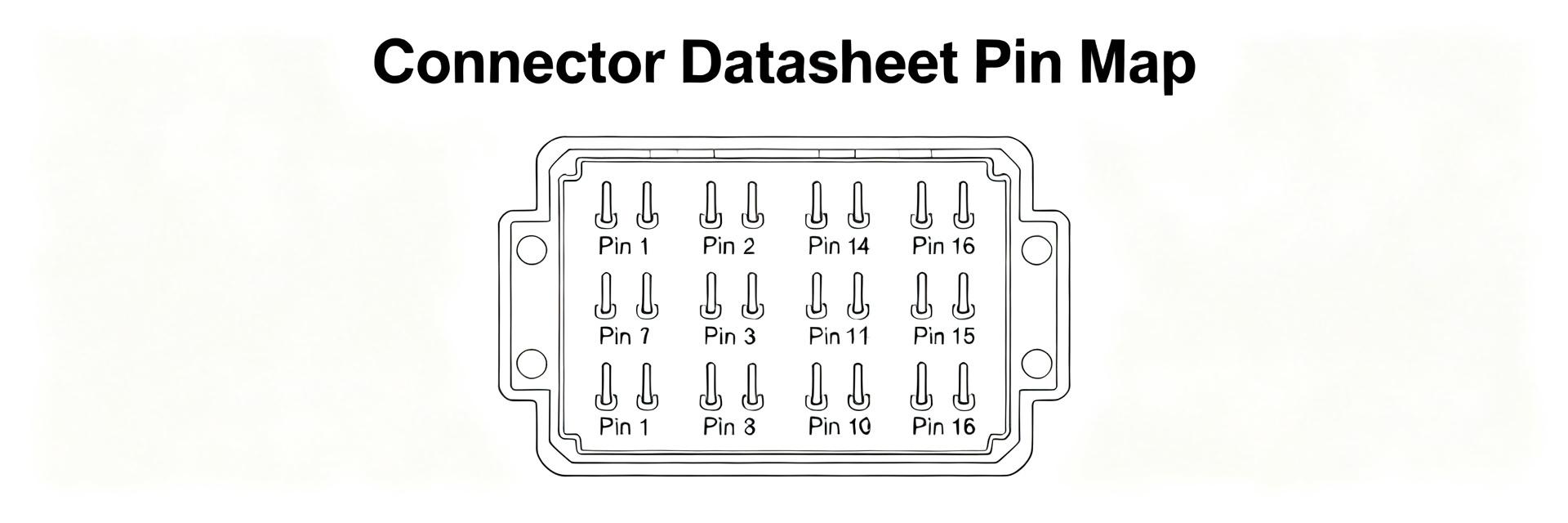

要点: 一貫したピンナンバリング規則とラベル付けされたネットの提案により、方向ミスを防止します。 根拠: 嵌合方向に沿ってキーのあるコーナーからピン番号を開始し、シルクスクリーンに非対称な機械的特徴を注記します。 説明: 組み立てとテストを簡素化するために、回路図にプレーンなピンマップとネット名の提案を含めてください。以下のマッピング例は、10ピンセグメントの典型的な信号/電源割り当てを示しています。

| ピン番号 | 機能 | 典型的な信号 / ネット名 |

|---|---|---|

| 1 | GND | GND |

| 2 | VCC | 3V3_SUPPLY |

| 3 | UART_RX | UART1_RX |

| 4 | UART_TX | UART1_TX |

| 5 | GPIO | GPIO_A |

2.2 PCBフットプリントの注記と不一致の回避

要点: ミラーリングされたフットプリントとパッドドリルの不整合は、適合問題の最も一般的な原因です。 根拠: パッドの極性と機械的なアンカーパッドを確認し、1:1のオーバーレイを印刷して嵌合サンプルまたはテストフィクスチャで適合を確認してください。 説明: 堅牢な統合のために、機械的なアンカーパッドを追加し、シルクスクリーンに方向をマークし、PCBメーカーおよびアセンブラとのレビュー手順に「53253-1270 PCBフットプリント」を含めてください。

電気的仕様と安全動作限界(データ分析)

3.1 電圧、定格電流、およびディレーティングガイダンス

要点: 信頼性を維持するために、連続動作には保守的なディレーティングを使用してください。 根拠: 接点が X アンペア(データシート参照)に定格されている場合、連続電流を定格値の 70–80% で設計し、接点あたり 1A を超える場合は銅箔面積またはビアを増やしてください。 説明: 例:2.0 A 定格の接点の場合、連続 1.4 A(70% ディレーティング)を計画し、パッドの下のサーマルビアで温度上昇を確認してください。

3.2 接触抵抗、絶縁、温度、および信頼性指標

要点: データシートから接触抵抗、絶縁耐力、嵌合サイクルを検査し、QAしきい値を設定してください。 根拠: 典型的な指標には、ミリオームレベルの接触抵抗、100 MΩ 超の絶縁抵抗、および指定された絶縁耐電圧が含まれます。 説明: 社内の合格/不合格しきい値:サイクルテスト後の接触抵抗の増加は初期値の 50% 以下、量産品の絶縁抵抗は 10 MΩ 以上とします。

設計統合:PCB、アセンブリ、およびEMIの考慮事項(メソッドガイド)

4.1 フットプリント、はんだ付け、およびアセンブリのベストプラクティス

要点: 一貫したはんだ接合を実現するために、パッド形状とステンシル開口部を最適化してください。 根拠: 該当する場合はピンインペーストの位置合わせのために長細いパッドを使用し、スルーホールスタイルのピンには標準的なペースト充填率の開口部に従ってください。 説明: パッドファイル、推奨ステンシル開口部、はんだプロファイル注記、およびチップ立ち(マンハッタン現象)やシャドウイングを防ぐための隣接部品のキープアウトゾーンを含むチェックリストをメーカー/アセンブラに提供してください。

4.2 EMI、シールド、および熱管理

要点: コネクタの配置とリターンパスは、EMIと信号整合性に影響を与えます。 根拠: コネクタに隣接するグラウンドステッチビアとインピーダンス制御されたトレースにより放射を低減し、銅箔ベタとビアアレイにより高電流時の熱性能を向上させます。 説明: 高速差動ペアはコネクタ端から離して配線し、3–4 mm ごとにグラウンドをステッチし、電流がディレーティング限界を超える場合は電源パッドの下にサーマルビアを使用してください。

テスト手順、検証チェックリスト、および調達に関する注記(ケース + アクション)

5.1 クイックテストとトラブルシューティングの手順

要点: アセンブリ後にコネクタを検証するための一連の簡単なテストを実行してください。 根拠: 導通マッピング、接触抵抗のスポットチェック、絶縁耐圧テスト、および機械的な嵌合/離脱力のチェックを実行します。 説明: 次の手順に従ってください:目視 → 導通 → 抵抗 → 絶縁 → 機械。具体的な手順については、ラボのセットアップで 53253-1270 コネクタをテストする方法の手順を参照してください。

| 症状 | 考えられる原因 | 即時チェック |

|---|---|---|

| 接触不良 | いもはんだ / ピンの曲がり | 目視 + 接点の抵抗チェック |

| 電源が入らない | ピン配置の誤配線 | ネットリストに対する電源ピンの導通 |

5.2 53253-1270 データシートで確認すべき事項と調達チェックリスト

要点: 購入前に機械図面、電気定格、メッキ、およびパッケージングを確認してください。 根拠: サプライヤーのドキュメントで推奨ランドパターン、メッキ/仕上げオプション、環境認定、および梱包方向を確認します。 説明: 最終的な寸法、電流/電圧値、および推奨PCBフットプリントについては、常に公式の 53253-1270 データシート をクロスチェックしてください。調達時のチェックには、リードタイム、MOQ、および梱包方向を含めてください。

まとめ

要点: ここにある凝縮されたピン配置マップと電気的制限を、1ページのレイアウトおよびテストリファレンスとして使用してください。 根拠: 主要な値とクイックテストを手元に置いておくことで、ボードの立ち上げ時の手直しを減らすことができます。 説明: 製造前に、すべての重要な数値を公式の 53253-1270 データシート と照合し、以下にリストされている短い検証テストを実行してください。

- 基板のシルクスクリーン上のピン番号と方向がピン配置と一致していることを確認します。誤配線を避けるためにネットに一貫してラベルを付けてください (53253-1270 ピン配置)。

- 連続電流を定格接点容量の 70–80% にディレーティングし、熱リリーフのために銅箔/ビアを追加します。

- 1:1のオーバーレイを印刷し、嵌合サンプルでフィットチェックを行います。フットプリントに機械的なアンカーを含めてください。

よくある質問

回路図の命名のために 53253-1270 のピン配置をどのように読めばよいですか?

要点: キーのあるコーナーまたは面取りされたコーナーから開始し、メーカーのナンバリング方向に合わせます。 根拠: 回路図とPCBの両方に同一のネット名を注記し、回路図シートに小さなインライン図を含めます。 説明: 一貫した命名(例:UART1_RX、3V3_SUPPLY)により、組み立てミスが最小限に抑えられ、テストマッピングが簡素化されます。

53253-1270 データシートのパラメータの最終的な値はどこにありますか?

要点: 公式データシートには、製造に必要な信頼できる機械的および電気的数値が含まれています。 根拠: 注文前にデータシートを使用してランドパターン、定格電流、および環境仕様を確認してください。 説明: データシートを調達の真実のソースとして扱い、BOMの部品番号とともにデータシートのリビジョンを記録してください。

コネクタの接触抵抗の迅速な合格/不合格しきい値は何ですか?

要点: 初期サンプルの測定値とデータシートの制限からしきい値を設定します。 根拠: 典型的な接触抵抗はミリオームレベルです。保守的なQAしきい値として、ライフサイクルテスト後の増加を 50% 以下に抑えます。 説明: 初品ユニットでベースライン抵抗を記録し、定期的なサンプルと比較します。しきい値を超える経年劣化があれば、根本原因分析のためにフラグを立てます。

- RM06F7683CT PCBフットプリントガイド:正確な0603パッドの作成

- RM 06 J 113 CT 0 6 0 3抵抗器:データ、仕様、および調達のヒント

- AT 93 C 56 B EEPROMデータシート:フルスペック&ピン配置ガイド

- AT 93 C 56 B EEPROM:仕様と実際の性能に関する考察

- 430 4 5-0 8 12コネクタ:アンプと電圧の仕様を1枚にまとめたシート

- 1mmFFC52271-1679:完全なスペックシートと購入ガイド

- PN 48 40 8-000 3技術データシート:完全な仕様の概要

- 16-02-0087圧着端子のデータシート:完全な仕様と評価

- 430 4 5-0 418データシートの内訳:仕様、ピン配置、サイズ

- 42815-0 1 1 4仕様レポート:電気的な評価と制限