-

- 連絡先

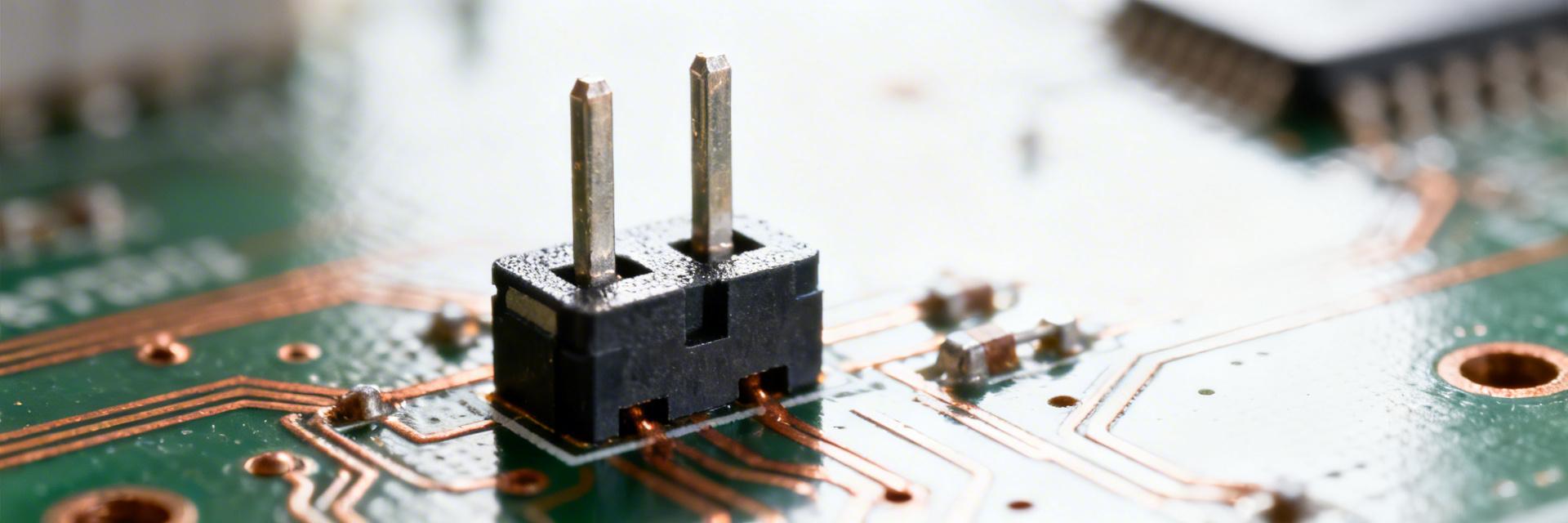

52465-1071 コネクタ:0.031インチピッチ&高さレポート

主な要点 (GEOサマリー)

- スペース効率:0.8mm (0.031in) ピッチにより、1.27mm 標準規格と比較して基板の水平占有面積を約30%削減します。

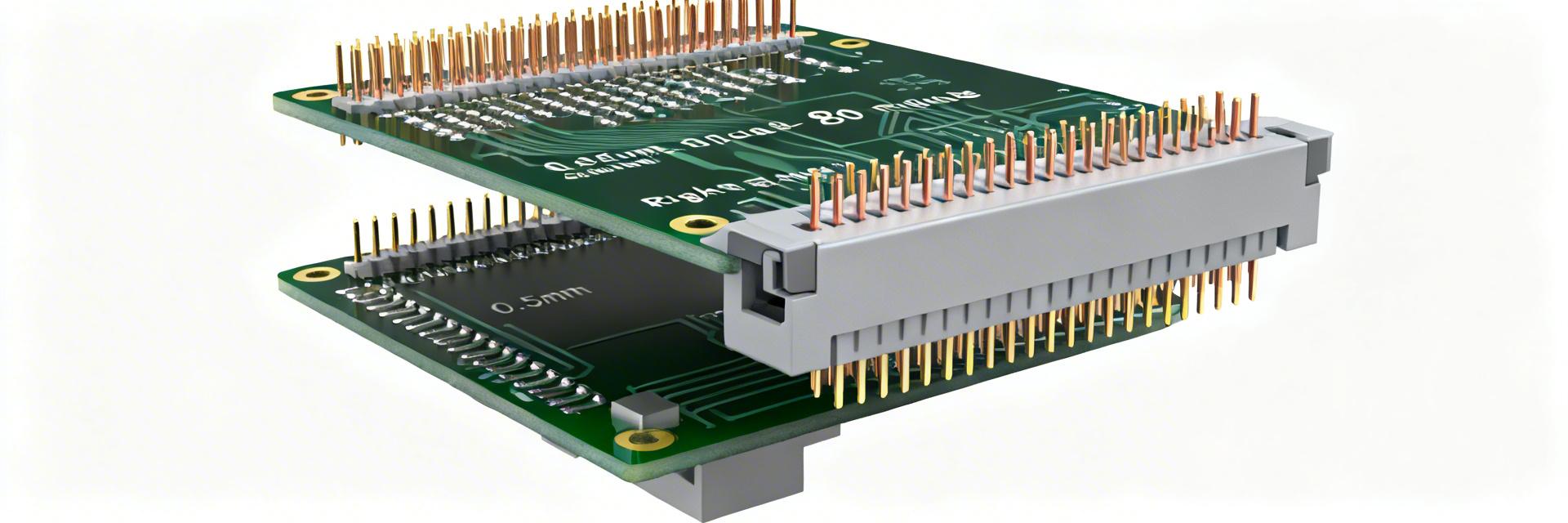

- 設計の柔軟性:4.5mmから7.0mmまでの嵌合高さにより、精密な垂直スタックの最適化が可能です。

- 信号整合性:SMT終端は高速データパスをサポートしますが、TDRによる検証が必要です。

- 生産歩留まり:高密度SMTレイアウトでは、99%以上の歩留まりを確保するためにAOIと精密なステンシル制御が不可欠です。

基板対基板接続の小型化により、コンパクトなコンシューマーおよび産業用システム向けに1.0mm未満のピッチの採用が広がっています。本概要では、52465-1071 コネクタファミリーの0.031in / 0.8 mmピッチと複数の嵌合高さオプションに焦点を当て、機械設計への影響、信号整合性のトレードオフ、製造容易性、およびプロトタイプから量産への移行に向けた調達アクションを分析します。

メリット:同一の直線スペース内でI/O密度を40%向上させ、ウェアラブルやIoTデバイスのPCB小型化を可能にします。

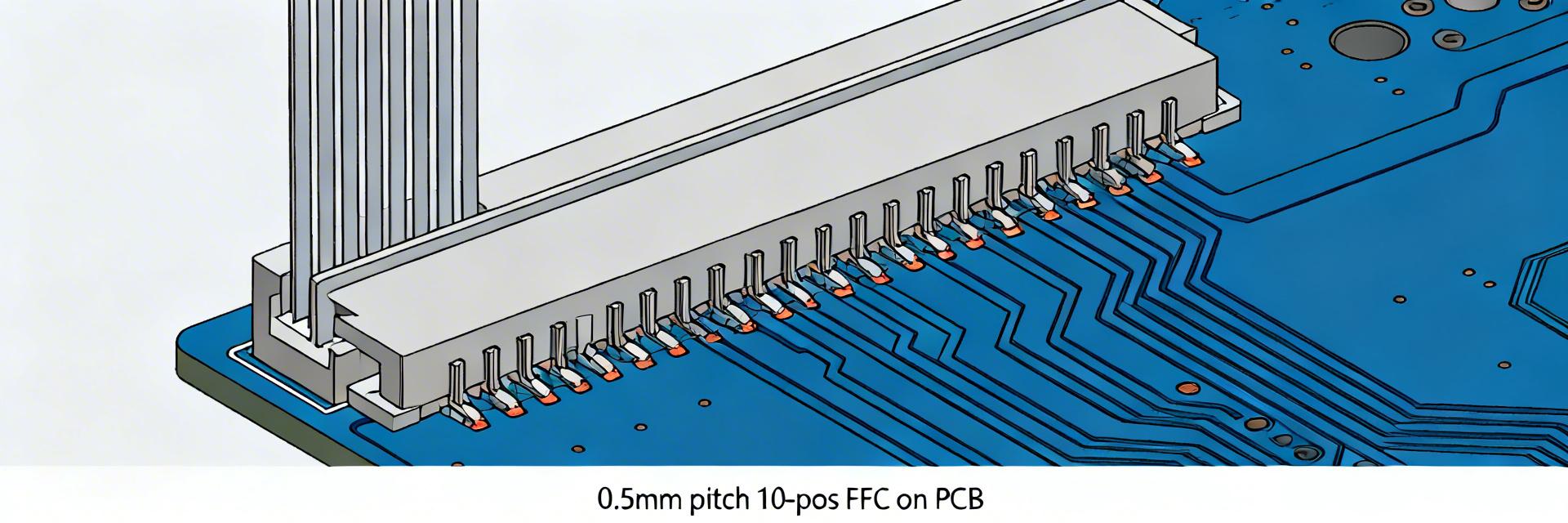

メリット:スルーホールを排除し、PCBの下層をコンポーネントの配線やシールドのために開放します。

コネクタの背景 — 52465-1071 の概要

基本仕様のスナップショット

ポイント:このコネクタは、薄型スタックアセンブリに最適化された単列表面実装基板対基板インターフェースです。エビデンス:代表的な製品では、0.031in / 0.8 mmピッチ、列長に合わせた極数の単列レイアウト、およびSMT終端が指定されています。解説:これらの属性により、基板面積が限られているが精密な配置とハンダ付け品質が要求されるメザニンスタックに適しています。設計者は選択前に、データシートで定格電圧/電流およびメッキオプションを確認する必要があります。

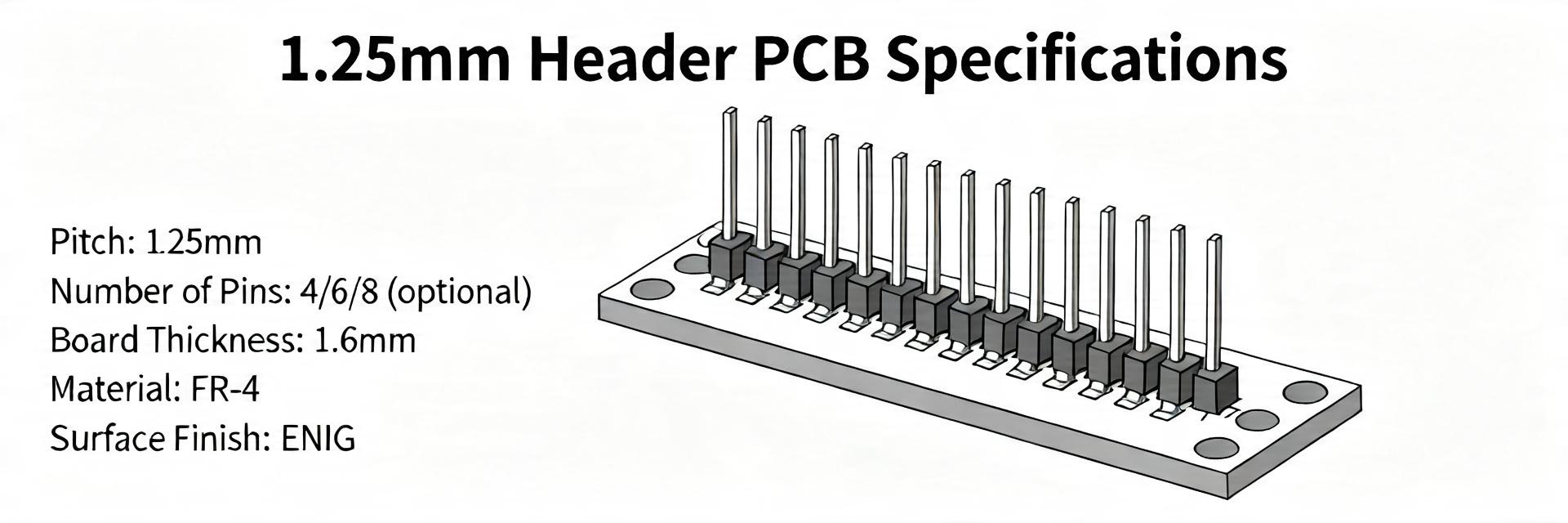

| 属性 | 52465-1071 シリーズ (0.8mm) | 一般的な 1.27mm ヘッダー | ユーザーの利点 |

|---|---|---|---|

| ピッチ | 0.031in (0.8 mm) | 0.050in (1.27 mm) | 36% のスペース節約 |

| 嵌合高さ | 4.5–7.0 mm | 固定 (~6.0mm) | モジュール式スタック制御 |

| 実装タイプ | SMT (表面実装) | THT または SMT | 自動マウンター対応 |

| 信号密度 | 高 (12.5 pins/cm) | 低 (7.8 pins/cm) | 多信号I/Oに最適 |

典型的なアプリケーションの文脈と制約

ポイント:薄型スタックモジュール、携帯型コンシューマー電子機器、垂直方向の密度が重要なコンパクト産業用モジュールなどが主な用途です。エビデンス:小ピッチにより基板の水平面積が削減され、よりタイトな基板スタックが可能になります。解説:0.031inピッチはスペースが限られた設計をサポートしますが、大電流パスや過酷な環境での使用には適していません。設計者は、特定の嵌合高さやメッキを選択する際、放熱、エンクロージャのクリアランス、および混在電源設計のための絶縁性を評価する必要があります。

ピッチの影響 — 0.031in ピッチ:電気的および機械的トレードオフ

信号整合性と電気的制限

ポイント:タイトなピッチはクロストークのリスクを高め、インピーダンス制御のための配線を制約します。エビデンス:0.031inピッチでは隣接するコンタクト間隔が狭まり、導体間の分離が制限されるため、差動ペアの間隔やリターンパスの設計に影響を与えます。解説:リターンパスの連続性に注意しながらマイクロストリップまたはストリップライン配線を使用し、可能な限りペア間隔を広げ、TDRやアイパターン・テストで検証してください。データシートに従ってピンあたりの電流を制限し、必要に応じて複数のピンに電力を分散させてください。

プリンシパル・インターコネクト・アーキテクト

"52465-1071 のような0.8mmピッチを扱う際、一般的な故障点はコンタクト領域への『はんだウィッキング』です。私は常に 0.1mmのステンシル厚 と1:1のアパーチャ比を推奨しています。スタックアップが許すなら、コネクタ遷移部でのループ面積を最小限に抑えるために、高速差動ペアを最上層のグランドプレーンの直下の層に配置してください。"

機械的許容差とアセンブリ歩留まり

ポイント:小ピッチは配置とはんだ付けの感度を高め、ブリッジやフィレット不全のリスクを増大させます。エビデンス:一般的なアセンブリ許容差は±0.05 mm以下に厳格化され、精密なペースト量の制御が必要になります。解説:より厳しいPCB製造許容差を指定し、ステンシル制御されたペースト塗布を行い、プロセスの早い段階でブリッジやボイドを検出するためにAOIや選択的X線検査ポイントを設けてください。PCBアセンブリ計画に受入基準を文書化してください。

高さバリエーション — 比較指標

| 指標 | 低い高さ (~4.5 mm) | 高い高さ (~7.0 mm) |

|---|---|---|

| スタック厚 | 最小化(超薄型デバイス) | 増加(モジュール式システム) |

| 機械的安定性 | 低い | 高い |

| 嵌合許容差 | 小さい | 許容範囲が広い |

| 耐振動性 | 補強が必要 | 本来の耐性が高い |

典型的な用途:ウェアラブル技術スタック

スマートウォッチのPCBアセンブリに4.5mmの高さバリエーションを使用し、EMIシールドのための10本の冗長グランドピンを維持しつつ、Z方向の高さを最小限に抑えます。

設計チェックリスト — 0.031in ピッチコネクタの統合

PCBレイアウトとフットプリントのベストプラクティス

ポイント:フットプリントの精度とはんだマスク戦略が、0.031inピッチでの歩留まりに直接影響します。エビデンス:狭いランドパターンでは、ブリッジを避けるためにソルダーマスクの拡張制御と正確なアニュラリングが必要です。解説:可能な限りメーカー推奨のランドパターンを使用してください。推奨がない場合は、パッドサイズの縮小、可能な限り0.15 mm以上の最小アニュラリング、ソルダーマスク定義パッドを採用し、ビアをパッド列のすぐ外側に配置するかキャップドビアを使用してください。隣接するコンポーネントのためのキープアウトゾーンと、嵌合アライメント機能のためのクリアランスを設けてください。

アセンブリと熱プロセスの考慮事項

ポイント:リフロープロファイルとペースト塗布が、濡れ性とチップ立ち(マンハッタン現象)のリスクに決定的な影響を与えます。エビデンス:ペースト量が不均一な小さなパッドは、リフロー中に濡れ不良やチップ立ちを引き起こします。解説:鉛フリープロセスに適したプリヒートとピーク温度を備えた制御されたリフロープロファイルを検証し、一貫したペースト量のためにステンシルの開口比を最適化してください。手はんだは修理のみに限定してください。リフロー後のAOI、隠れた接合部のためのX線検査、およびアセンブリ文書に定義された修理ワークフローを含めてください。

要約(結論と次のステップ)

主な調査結果:0.031inピッチコネクタファミリーは、基板スタックの大幅な高密度化と柔軟な嵌合高さをサポートしますが、より厳しいPCB製造許容差、厳格なペースト塗布、および重点的な信号整合性/機械検証計画を必要とします。

- PCBリリースの前に、データシートと3Dモデルでピッチとフットプリントの寸法を確認してください。0.031inピッチのクリアランスとパッド形状が確定していることを確実にしてください。

- 利用可能な高さ全体で評価用サンプルを注文し、嵌合サイクルと接触抵抗の追跡調査を行い、信頼性と信号マージンに対するライフサイクルの影響を評価してください。

- 信号整合性と機械的堅牢性を定量化するために、TDR/アイパターン・テストおよび機械的衝撃/振動プロファイルを検証計画に組み込んでください。

FAQ — よくある質問

ピッチが小さくなると、ペアの間隔やリターンパスの連続性のためのスペースが減り、クロストークのリスクが高まります。内層ストリップライン配線、可能な範囲でのペア間隔の拡大で対策し、許容可能なマージンを確認するためにTDRとアイパターン・テストで検証してください。

機械的レバレッジと嵌合許容差を改善するために、中間から高めの嵌合高さを選択し、コンタクトのストレスを軽減するためにアライメントボスや補強を追加してください。合格/不合格基準を確立するために、振動および衝撃試験で確認してください。

ピッチ (0.031in / 0.8 mm)、利用可能な嵌合高さ、メッキとはんだ付け性の詳細、3D STEPファイル、および各高さバリエーションのサンプルキットをデータシートで確認するよう依頼してください。初回製品検査のための検査基準も含めてください。

- RM06F7683CT PCBフットプリントガイド:正確な0603パッドの作成

- RM 06 J 113 CT 0 6 0 3抵抗器:データ、仕様、および調達のヒント

- AT 93 C 56 B EEPROMデータシート:フルスペック&ピン配置ガイド

- AT 93 C 56 B EEPROM:仕様と実際の性能に関する考察

- 430 4 5-0 8 12コネクタ:アンプと電圧の仕様を1枚にまとめたシート

- 1mmFFC52271-1679:完全なスペックシートと購入ガイド

- PN 48 40 8-000 3技術データシート:完全な仕様の概要

- 16-02-0087圧着端子のデータシート:完全な仕様と評価

- 430 4 5-0 418データシートの内訳:仕様、ピン配置、サイズ

- 42815-0 1 1 4仕様レポート:電気的な評価と制限

-

HCPL2601onsemiOPTOISO 2.5KV OPN COLL 8-DIP

HCPL2601onsemiOPTOISO 2.5KV OPN COLL 8-DIP -

MCT6onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP

MCT6onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP -

C3PPT-2618MCW IndustriesIDC CABLE - CPC26T/AE26M/CPC26T

C3PPT-2618MCW IndustriesIDC CABLE - CPC26T/AE26M/CPC26T -

C3PPT-2606GCW IndustriesIDC CABLE - CPC26T/AE26G/CPC26T

C3PPT-2606GCW IndustriesIDC CABLE - CPC26T/AE26G/CPC26T -

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T -

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X -

S6008LLittelfuse Inc.SCR 600V 8A TO220

S6008LLittelfuse Inc.SCR 600V 8A TO220