-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

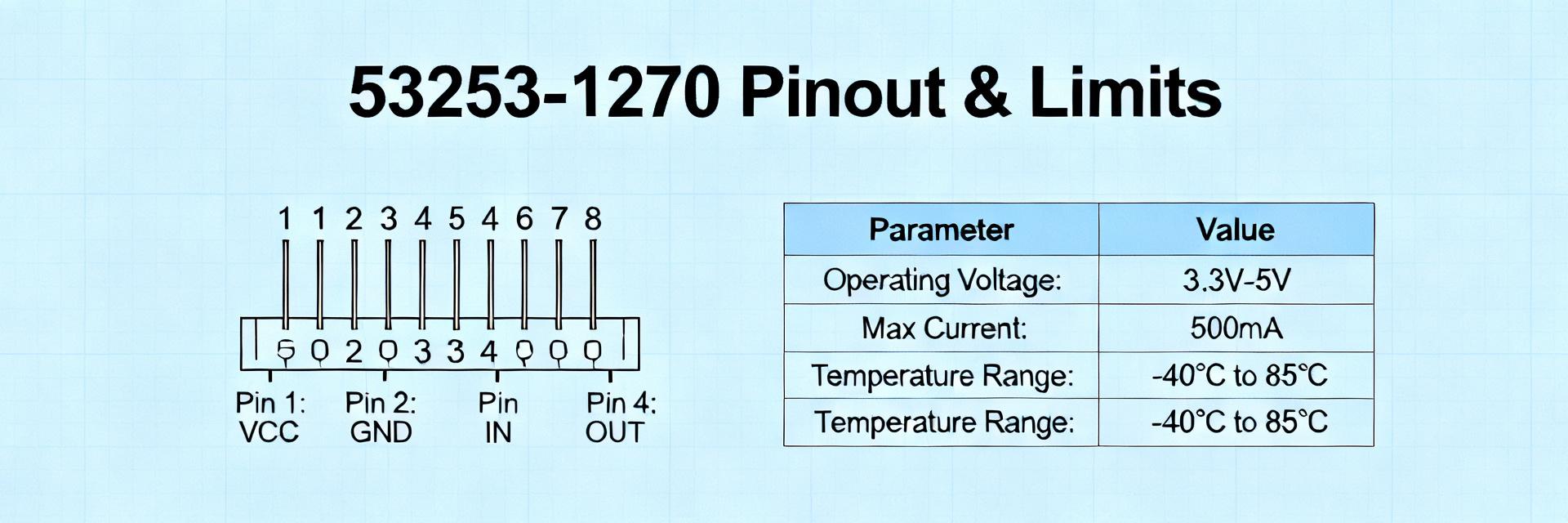

53253-1270 Pinout & Electrical Summary — Quick Data Pack

Point: This quick data pack compresses the essential 53253-1270 pinout and electrical limits so designers can speed layout and verification.

Evidence: Condensed references and common verification steps reduce iteration time on average for connector integration projects.

Explanation: Use the single-page map below during schematic capture, footprint creation and first-board bring-up to avoid orientation errors and late rework.

Point: The document focuses on practical, testable items rather than full certification detail. Evidence: For final procurement and qualification, always cross-check values against the official 53253-1270 datasheet. Explanation: Treat the pack as a fast reference for design decisions; keep the datasheet at hand for buy-off and compliance checks.

Part overview & typical applications (Background)

1.1 Part ID, common variants & typical uses

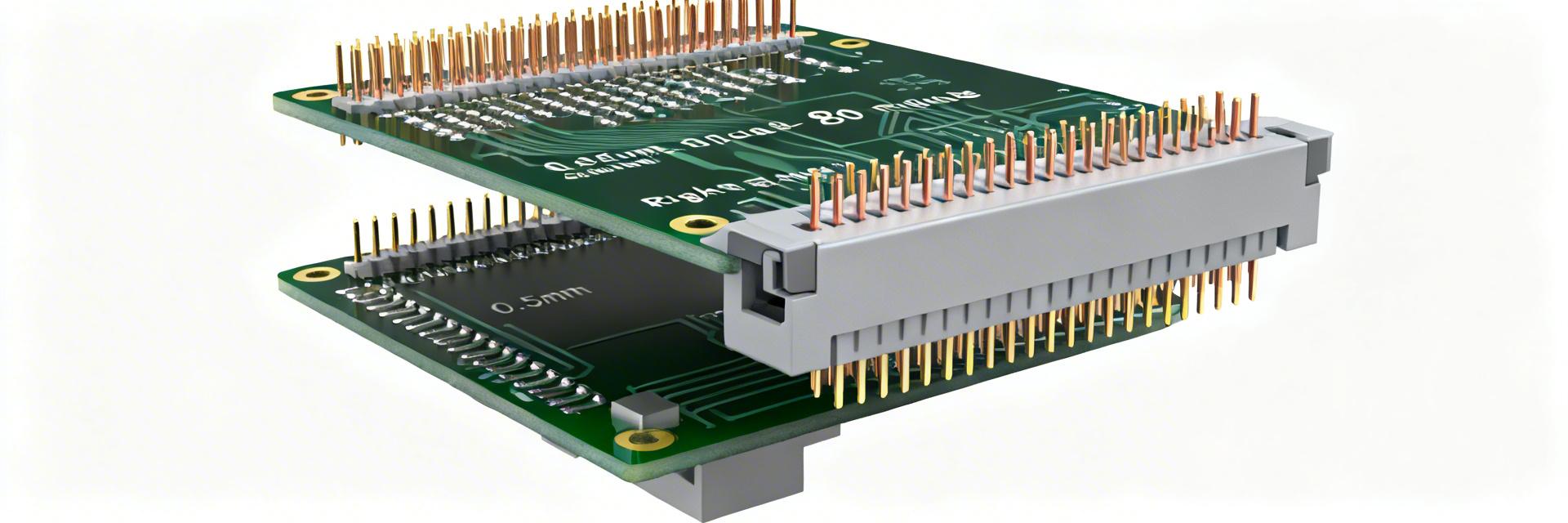

Point: The 53253-1270 is a low-profile rectangular header family with 2.00 mm pitch commonly used as board-to-board and wire-to-board signal interconnect. Evidence: Variants include straight vs right-angle and shrouded vs open housings; row counts vary by mating configuration. Explanation: Typical uses are mid-density I/O, signal headers for control boards, and low-current power distribution in compact assemblies.

- Use-cases: board-to-board mezzanine, cable harness interfaces, test jigs, and discrete signal breakout headers.

Note: refer to the official 53253-1270 datasheet for ordering codes and mechanical drawings.

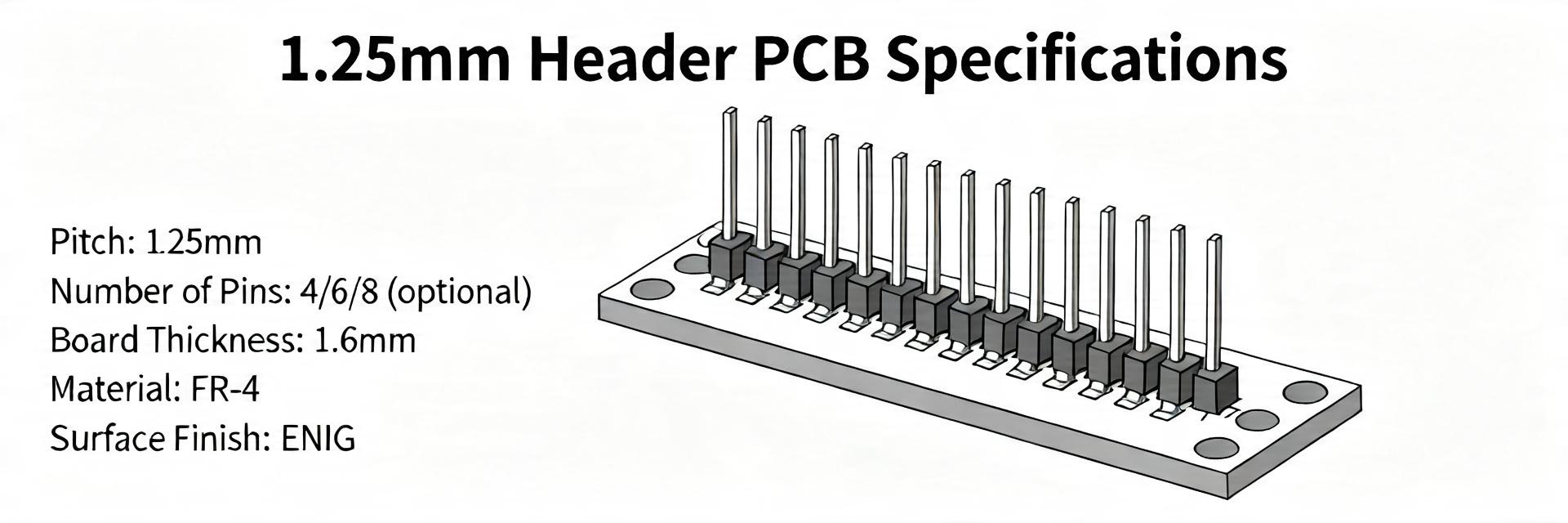

1.2 Key mechanical dimensions & footprint summary

Point: Critical dimensions affecting PCB layout are pitch, row spacing, pin protrusion and body height. Evidence: Designers should extract pitch (nominal 2.00 mm), expected pin length from PCB to mating surface, and keep-out height for adjacent components. Explanation: Create a dimension table and a simple top/side sketch for quick placement and collision checks before routing.

| Dimension | Nominal | Tolerance |

|---|---|---|

| Pitch | 2.00 mm | ±0.10 mm |

| Row spacing | — (varies by variant) | see datasheet |

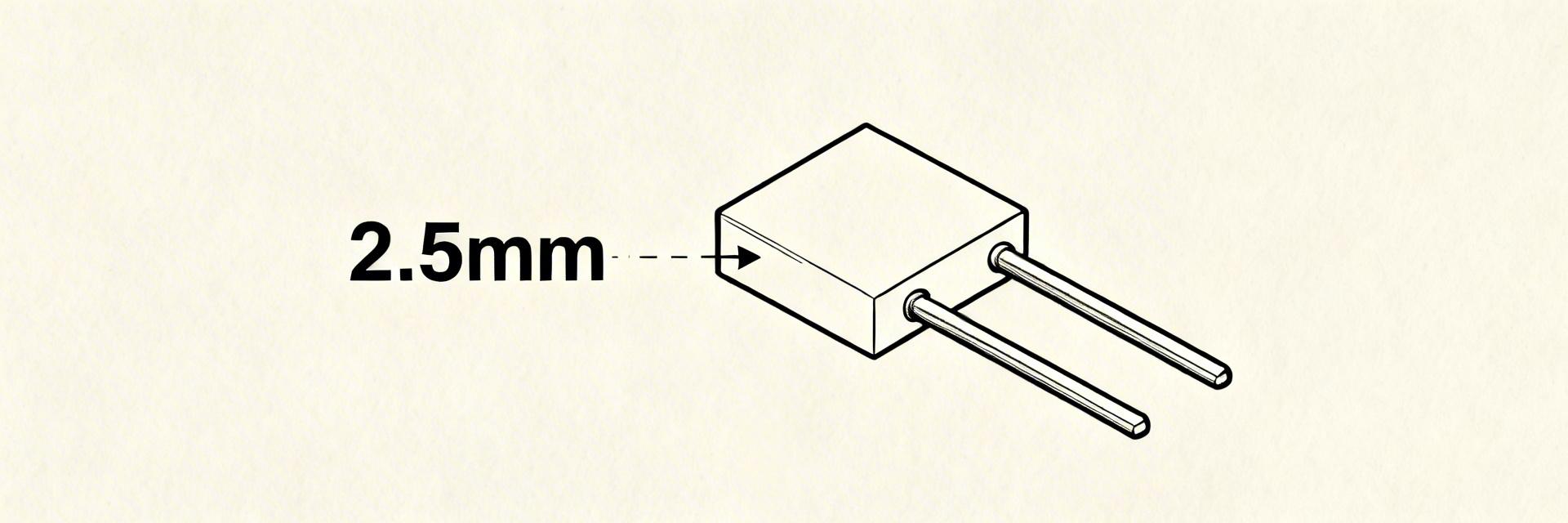

| Pin length (to PCB) | ~2.5–4.0 mm | ±0.2 mm |

Pinout mapping & numbering logic (Data analysis)

2.1 Pin numbering diagram & signal assignment

Point: A consistent pin numbering convention and labeled net suggestions prevent orientation errors. Evidence: Number pins starting from the keyed corner following the mating direction; annotate asymmetric mechanical features on the silkscreen. Explanation: Include a plain pin map on the schematic and a net-name suggestion to simplify assembly and test — example mapping below shows typical signal/power assignment for a 10-pin segment.

| Pin # | Function | Typical signal / Net name |

|---|---|---|

| 1 | GND | GND |

| 2 | VCC | 3V3_SUPPLY |

| 3 | UART_RX | UART1_RX |

| 4 | UART_TX | UART1_TX |

| 5 | GPIO | GPIO_A |

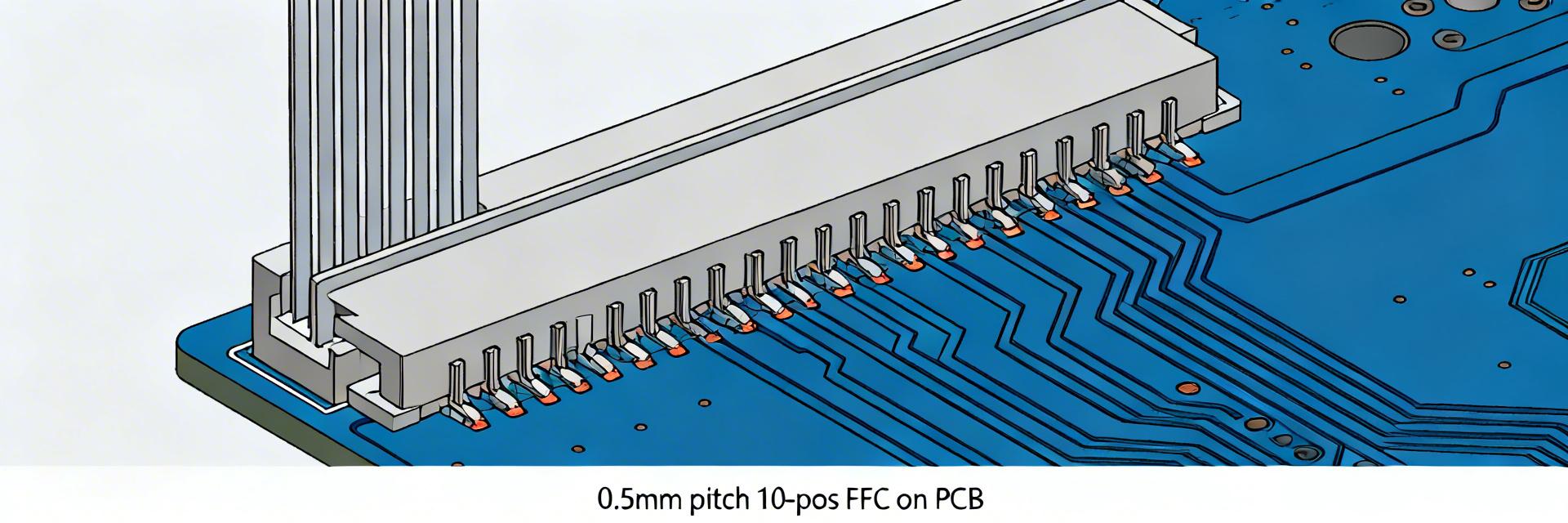

2.2 PCB footprint notes & mismatch avoidance

Point: Mirrored footprints and pad-drill misalignment are the most common causes of fit issues. Evidence: Verify pad polarity and mechanical anchor pads; print a 1:1 overlay and fit with a mating sample or test fixture. Explanation: For robust integration, add mechanical anchor pads, mark orientation on silkscreen, and include "53253-1270 PCB footprint" in review steps with PCB fab and assembler.

Electrical specifications & safe operating limits (Data analysis)

3.1 Voltage, current ratings and derating guidance

Point: Use conservative derating for continuous operation to maintain reliability. Evidence: If a contact is rated for X amps (refer to datasheet), design continuous currents at 70–80% of rated value and increase copper area or vias for >1A per contact. Explanation: Example: for a rated 2.0 A contact, plan for 1.4 A continuous (70% derate) and verify temperature rise with thermal vias under the pad.

3.2 Contact resistance, insulation, temperature & reliability metrics

Point: Inspect contact resistance, dielectric strength and mate cycles from the datasheet and set QA thresholds. Evidence: Typical metrics include milliohm-level contact resistance, >100 MΩ insulation resistance, and specified dielectric withstanding voltage. Explanation: In-house pass/fail thresholds: contact resistance increase ≤50% over initial reading after cyclic test; insulation resistance above 10 MΩ for production units.

Design integration: PCB, assembly & EMI considerations (Method guide)

4.1 Footprint, soldering and assembly best practices

Point: Optimize pad geometry and stencil apertures to achieve consistent solder joints. Evidence: Use elongated pads for pin-in-paste alignment where applicable, and follow standard paste % apertures for through-hole-style pins. Explanation: Provide a checklist to the fab/assembler including pad files, recommended stencil apertures, solder profile notes and keep-out zones for adjacent parts to prevent tombstoning or shadowing.

4.2 EMI, shielding and thermal management

Point: Connector placement and return paths influence EMI and signal integrity. Evidence: Ground stitching vias adjacent to the connector and controlled impedance traces reduce emissions; copper pours and via arrays improve high-current thermal performance. Explanation: Route high-speed differential pairs away from the connector edge, stitch grounds every 3–4 mm, and use thermal vias under power pads when currents exceed derated limits.

Test procedures, verification checklist & sourcing notes (Case + Action)

5.1 Quick test and troubleshooting steps

Point: Execute a short set of tests post-assembly to validate connectors. Evidence: Run continuity mapping, contact resistance spot checks, dielectric insulation testing and mechanical mate/unmate force checks. Explanation: Follow the step sequence: visual → continuity → resistance → insulation → mechanical; for guidance on practical steps, consult procedures for how to test 53253-1270 connector in your lab setup.

| Symptom | Probable cause | Immediate check |

|---|---|---|

| Intermittent contact | Cold solder joint / bent pin | Visual + resistance check at contact |

| No power | Mis-wired pinout | Continuity to supply pins vs netlist |

5.2 What to confirm on the 53253-1270 datasheet & procurement checklist

Point: Verify mechanical drawings, electrical ratings, plating and packaging before purchase. Evidence: Confirm recommended land pattern, plating/finish options, environmental qualifications and pack orientation on supplier docs. Explanation: Always cross-check the official 53253-1270 datasheet for final dimensions, current/voltage numbers and recommended PCB footprint; include lead-time, MOQ and packaging orientation in procurement checks.

Summary

Point: Use the condensed pinout map and electrical limits here as your single-page layout and test reference. Evidence: Keeping the key values and quick tests at hand reduces rework during board bring-up. Explanation: Before production, verify every critical number against the official 53253-1270 datasheet and execute the short verification tests listed below.

- Confirm pin numbering and orientation on board silkscreen to match pin mapping; label nets consistently to avoid mis-wiring (53253-1270 pinout).

- Derate continuous current to 70–80% of rated contact ampacity and add copper/vias for thermal relief.

- Print a 1:1 overlay and perform fit-check with a mating sample; include mechanical anchors on the footprint.

Frequently Asked Questions

How do I read the 53253-1270 pinout for schematic naming?

Point: Start from the keyed or chamfered corner and follow the manufacturer numbering direction. Evidence: Annotate both schematic and PCB with identical net names and include a small inline diagram on the schematic sheet. Explanation: Consistent naming (e.g., UART1_RX, 3V3_SUPPLY) minimizes assembly errors and simplifies test mapping.

Where can I find final values for 53253-1270 datasheet parameters?

Point: The official datasheet contains the authoritative mechanical and electrical values necessary for production. Evidence: Use the datasheet to extract land-pattern, current ratings, and environmental specs before ordering. Explanation: Treat the datasheet as the source of truth for procurement, and record the datasheet revision alongside the part number in your BOM.

What are quick pass/fail thresholds for connector contact resistance?

Point: Establish thresholds from initial sample measurements and datasheet limits. Evidence: Typical contact resistance is milliohm-level; allow ≤50% increase after life-cycle testing as a conservative QA threshold. Explanation: Log baseline resistance on first article units and compare periodic samples; flag any aging above threshold for root-cause analysis.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- PE51113-2 Antenna Performance Report: Vehicle Metrics

- PE51113-4 Datasheet Deep Dive: Gain, VSWR & Specs Explained

- PE51113-2 Antenna Performance Report: Specs & Gains

- PE51113-2 Datasheet Analysis: Mobile Antenna Specs & Metrics

- PE51113-4 Performance Report: Gain, Bandwidth, Specs

- AANI-FB-0174-1 Performance: Measured Gain & Efficiency

- AANI-FB-0032-1 FPC Antenna: Lab-Tested Performance Insights

-

HCPL2601onsemiOPTOISO 2.5KV OPN COLL 8-DIP

HCPL2601onsemiOPTOISO 2.5KV OPN COLL 8-DIP -

MCT6onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP

MCT6onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP -

C3PPT-2618MCW IndustriesIDC CABLE - CPC26T/AE26M/CPC26T

C3PPT-2618MCW IndustriesIDC CABLE - CPC26T/AE26M/CPC26T -

C3PPT-2606GCW IndustriesIDC CABLE - CPC26T/AE26G/CPC26T

C3PPT-2606GCW IndustriesIDC CABLE - CPC26T/AE26G/CPC26T -

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T -

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X -

S6008LLittelfuse Inc.SCR 600V 8A TO220

S6008LLittelfuse Inc.SCR 600V 8A TO220